- 我的订阅

- 科技

我们正处于一个信息大暴发的时代,每天都能产生数以百万计的新闻资讯!

虽然有大数据推荐,但面对海量数据,通过我们的调研发现,在一个小时的时间里,您通常无法真正有效地获取您感兴趣的资讯!

头条新闻资讯订阅,旨在帮助您收集感兴趣的资讯内容,并且在第一时间通知到您。可以有效节约您获取资讯的时间,避免错过一些关键信息。

台积电:2030年量产1nm、可封装1万亿个晶体管

2023-12-28 15:31:48 作者:姚立伟

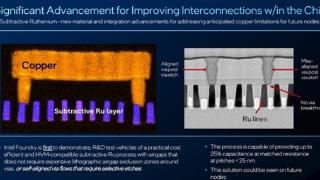

12月28日,IEDM 2023国际电子元件会议上,台积电发布了其半导体制造工艺和封装技术的路线图。该公司计划在接下来的几年内推出一系列先进的工艺节点和技术。

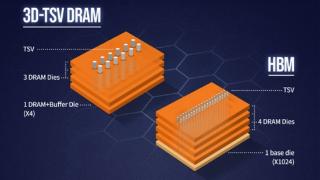

目前,台积电正在推进3nm级别的N3系列工艺,并计划在2025-2027年间推出更先进的N2系列工艺。这一系列工艺将集成超过1000亿个晶体管,并通过CoWoS、InFO和SoIC等多种封装技术实现。此外,台积电还计划使用EUV光刻、金属氧化物ESL等新材料和新技术。

更令人期待的是,台积电还规划了1.4nm级别的A14和1nm级别的A10工艺节点。虽然这两个命名与Intel的A20和A18相似,但它们被认为是更“先进”的。其中,A10工艺节点计划于2030年左右量产,单颗芯片内集成超过2000亿个晶体管,单个封装内则超过1万亿个晶体管,相比N2工艺翻一倍。

有趣的是,英特尔也计划在2030年实现单个封装中的1万亿个晶体管。这似乎是一个挑战性的目标。

目前,最复杂的单芯片是NVIDIA GH100,拥有800亿个晶体管。而在多芯片封装方面,各种GPU计算芯片处于领先地位。例如,Intel Ponte Vecchio GPU Max已超过1000亿个晶体管,而AMD Instinct MI300A和MI300X分别有1460亿个和1530亿个晶体管。

通过不断推陈出新和技术进步,台积电将继续引领半导体行业的发展,并为用户带来更强大、更高效的电子产品体验。 返回搜狐,查看更多

责任编辑:

以上内容为资讯信息快照,由td.fyun.cc爬虫进行采集并收录,本站未对信息做任何修改,信息内容不代表本站立场。

快照生成时间:2023-12-28 20:46:04

本站信息快照查询为非营利公共服务,如有侵权请联系我们进行删除。

信息原文地址: