- 我的订阅

- 科技

我们正处于一个信息大暴发的时代,每天都能产生数以百万计的新闻资讯!

虽然有大数据推荐,但面对海量数据,通过我们的调研发现,在一个小时的时间里,您通常无法真正有效地获取您感兴趣的资讯!

头条新闻资讯订阅,旨在帮助您收集感兴趣的资讯内容,并且在第一时间通知到您。可以有效节约您获取资讯的时间,避免错过一些关键信息。

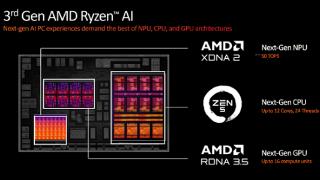

AMD Zen5大小核锐龙8050第一次现身!

Intel12代酷睿引入了异构大小核,AMD搞的则是同构大小核,并已在现有的锐龙7040U系列上做了尝试,使用Zen4、Zen4c的组合,下一代的锐龙8000系列移动版上将升级为Zen5、Zen5的搭档。

根据此前传闻,代号StrixPoint的锐龙8050系列,将会配备最多4个Zen5、8个Zen5c核心,同时集成16个CU单元的RDNA3.5GPU、算力翻番到20TOPS的二代锐龙AI引擎,热设计功耗范围依然是28-54W。

今天在网上看到了疑似锐龙8050处理器的CPU-Z、HWiNFO截图,可以看到大量基本信息,尤其是4个大核、8个小核,而且都支持多线程技术,都支持AVX-512指令集。

这两点,正是Intel大小核架构的致命缺陷。

无论Zen5还是Zen5c,每个核心的一级缓存都是完全一样的,均包括32KB指令缓存、48KB数据缓存,二级缓存则是每个大核单独1MB,每四个小核共享1MB,最后所有核心共享三级缓存(容量检测冲突疑为16MB)。

这种缓存体系,倒是和Intel的设计颇为相似。

不过最低6.3GHz、最高8.8GHz的频率,明显是检测错误,毕竟现在还是工程样品阶段。

总之,AMD这种同构大小核看起来更加合理一些,性能和功能更完整,也能让系统、软件更好地适配支持。

以上内容为资讯信息快照,由td.fyun.cc爬虫进行采集并收录,本站未对信息做任何修改,信息内容不代表本站立场。

快照生成时间:2023-08-12 09:45:07

本站信息快照查询为非营利公共服务,如有侵权请联系我们进行删除。

信息原文地址: