- 我的订阅

- 科技

我们正处于一个信息大暴发的时代,每天都能产生数以百万计的新闻资讯!

虽然有大数据推荐,但面对海量数据,通过我们的调研发现,在一个小时的时间里,您通常无法真正有效地获取您感兴趣的资讯!

头条新闻资讯订阅,旨在帮助您收集感兴趣的资讯内容,并且在第一时间通知到您。可以有效节约您获取资讯的时间,避免错过一些关键信息。

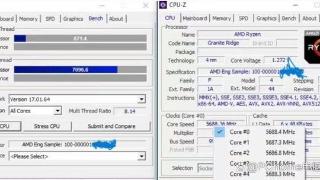

AMD Strix Point再次现身基准测试

AMD今年将带来全新的Zen5系列架构,推出Ryzen9000系列产品。其中代号StrixPoint的APU采用了混合架构设计,去年已经有ES芯片出现在基准测试的数据库里,上个月还出现在AMD的发货清单上。

据Wccftech报道,近日StrixPoint再次现身,出现在Geekbench基准测试里。信息显示其属于StrixPoint(1)芯片,拥有12核心24线程,L1指令缓存为32KB,L1数据缓存为48KB,L2缓存为12MB(每核心对应1MB),L3缓存为24MB(系统只显示了Zen5内核对应的16MB),TDP为28W,属于专为移动设备设计的FP8平台。相比于Zen4架构内核,L1数据缓存的容量提升了50%。

日志文件提示APU的核心频率为1.4GHz,应该也是早期做测试的ES版本。在单核基准测试里,这块StrixPointES芯片的成绩为1217分,多核基准测试里则是8016分。虽然核心频率不高,但是成绩不错,特别是多核基准测试的表现。

根据之前流传的信息,StrixPoint会有两种设计:一种是普通的单芯片设计,为StrixPoint(1)芯片,CPU部分为4×Zen5+8×Zen5c的配置,GPU部分的CU数量将增加至16个,基于RDNA3.5/3+架构的CU,集成XDNA2架构“RyzenAI”引擎;另外一种可能被称为“StrixPointHalo”,或者也称为“StrixHalo”或者“Sarlak”,是一款高端APU,采用了chiplet设计,为StrixPoint(2)芯片,CPU部分最多拥有16核心,CU数量增至40个。

前一段时间有内部人士提供了StrixPoint(1)芯片的在3DMarkTimeSpy里的成绩,显示可以提供与入门级独立显卡相当的图形性能。

以上内容为资讯信息快照,由td.fyun.cc爬虫进行采集并收录,本站未对信息做任何修改,信息内容不代表本站立场。

快照生成时间:2024-04-25 00:45:11

本站信息快照查询为非营利公共服务,如有侵权请联系我们进行删除。

信息原文地址: